3rd Workshop on

Highly Parallel Processing on a Chip (HPPC 2009)

August 25, 2009, Delft, The Netherlands

in conjunction with

August 25-28, 2009, Delft, The Netherlands.

AIMS AND SCOPE

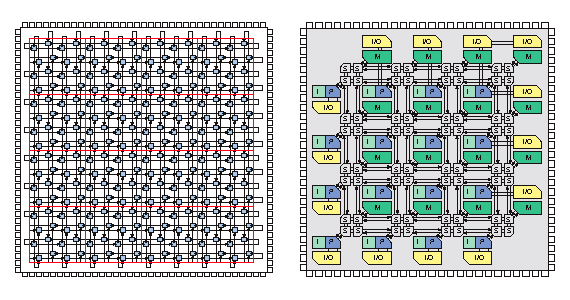

The decline in the growth of single-processor performance, the growing concerns

with energy consumption, and the still exponential increase in transistors per

chip as per Moore's law, will open the scene for single-chip processors with a

substantial amount of parallelism to meet the demands for extremely high

performance, reliability, and controlable power consumption in all areas of

computing. The major challenge for the coming years will be the design of

architectures supporting manageable programming abstractions to allow the

mainstream programmer to take advantage of the processing power promised by the

technological developments.

HPPC, the third workshop in the series, co-located with the EuroPar conference,

is *the* workshop dedicated to addressing all aspects of highly parallel

processing on a chip, be it in existing or emerging multi-core designs, or in

bold, new proposals for architectures, programming models, languages and

libraries for managing and exploiting massive levels of parallelism on a chip. Particular emphasis is on the interaction between hardware, architecture

(processors, on-chip networks, cache and memory system), programming models and

languages, and algorithms as well as applications in need of significant

amounts of single-chip parallelism. The workshop will be conducted in an

informal atmosphere, stressing interaction and discussion between presenters

and audience.

Topics of interest include, but are not limited to

° hardware techniques (e.g. power saving, clocking, fault-tolerance)

° processor core architectures (homogeneous and heterogeneous)

° special purpose processors (accelerators, GPUs)

° on-chip memory and cache (or cache-less) organization, and interconnects

° off-chip memory, I/O, and multi-core interconnects

° overall system design (resource allocation and balancing)

° programming models (e.g. PRAM, BSP, data parallel, vector, transactional)

° languages and software libraries

° implementation techniques (e.g. multi-threading, work-stealing)

° support and performance tools, performance evaluation

° parallel algorithms and applications

° migration of existing codebase

° teaching of parallel computing

for/on highly parallel multi-core systems.

Authors are encouraged to submit original, unpublished research or overviews addressing issues in the design and application of highly parallel

multi-core processors as outlined above.

Submission:

June 19, 2009

Notification:

July 20, 2009

Workshop:

August 25, 2009

Final LNCS paper:

September, 2009

Registration:

via Euro-Par

Contact:

chair@hppc-

workshop.org

Last updated September 14, 2009, MF